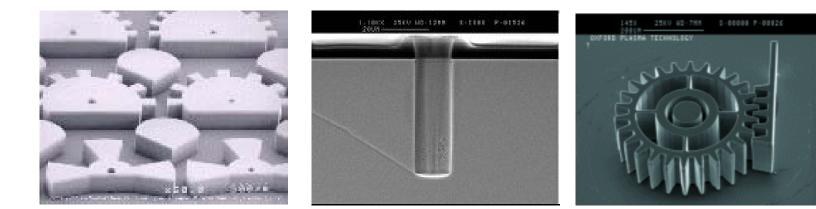

# A Deep Silicon RIE Primer Bosch Etching of Deep Structures in Silicon

April 2009

## **A Deep Silicon RIE Primer**

#### 1.0) Etching:

Silicon does not 'naturally' etch anisotropically in fluorine based chemistries. Si etches isotropically in CF4, SF6 and other fluorine based chemistries. To achieve anisotropic etching, a variety of process 'tricks' have been developed. The most commonly used trick is the Bosch process (the others being cryo-processing and 'black' silicon).

The Bosch process is a patented process developed by Bosch Inc (the German car parts manufacturer). It is patented, which means a Bosch ready ICP RIE costs an extra \$30,000 to \$50,000 US for patent licencing.

The process Bosch consists of two steps:

<u>Coating the entire surface with 'polymer'.</u> A teflon-like substance formed in the plasma from the C4F8 gas. (Typically 10 second 'deposition')

The C4F8 is turned off and SF6 is let into the chamber. <u>The SF6 plasma etches</u> the polymer in the bottom of the trench and once that is removed, the <u>Silicon</u> below the polymer. The SF6 etch of silicon is isotropic. The SF6 does not etch the polymer on the walls because to etch polymer requires both radicals and ions. (typically 15 second etch)

3) A single cycle will etch 0.5 to 1 um. <u>This cycle is repeated until the structure has been etched</u>

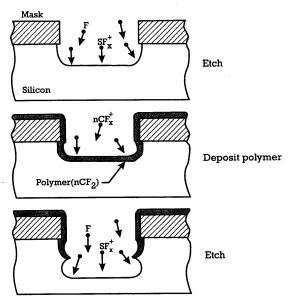

**Figure 3.12** Profile of a deep reactive ion etched (DRIE) trench using the Bosch process. The process cycles between an etch step using  $SF_{e}$  gas, and a polymer deposition step using  $C_{4}F_{e}$ . The polymer protects the sidewalls from etching by the reactive fluorine neutrals. The scalloping effect of the etch is exaggerated.

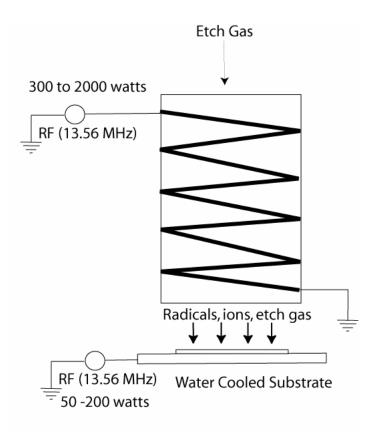

## 2.0) Etching Tool: ICP RIE

Figure 2 shows a schematic diagram of a basic ICP RIE etch tool. This etch tool consists of two plasma sources:

1) an ICP source to generate high densities of ions and neutrals for etching (over 90% of feedgas becoming either radicals or ions)

2) a RF powered chuck that contains the wafer (the "RIE" section). The RIE section controls the energy of the ions which bombard the substrate.

This machine is different than 'normal' RIEs, because within this machine the ion and neutral generation are independent of the ion bombardment energy. In typical RIEs, these two functions are performed in the same plasma (the RF plasma on the chuck). The reason why all RIEs are not ICP RIEs (given their obvious advantages) is cost. A used RIE is \$25,000 US and a ICP RIE is \$200,000 to \$600,000 US.

## 3.0) Etching Parameters

- *Etch Rate:* 0.5 to 2.0 um/minute (depends on etch recipe)

- Masking Layers:

a) Photoresist --- sufficient if etching less than 30 um

b) PECVD or Thermal Oxide (SiO2) - 0.6 um thermal oxide sufficient for 200um + etches (though actual thickness required for the deeper etches depends on etch recipe)

c) Metal thin film (Cr, etc) --- 0.2 um sufficient for 300 um+ deep etches - *Sidewalls:* Scalloped shaped and 85 to 92 degrees (not perfectly normal to the surface)

## 4.0) Real Process Issues (Things you will actually need to worry about)

1) Each DRIE etch is unique. For a different etch depth or mask layout, the process will need to be optimized for the new design or etch depth. "A 200 um deep etch is NOT a 20 um etch done 10 times longer". The deeper etch will not reach 200 um, but rather reach an intermediate depth and stop. This is possibly due to Aspect Ratio Dependant Etching or an increase in the surface area of the wafer as the etch depth becomes large (100's of microns)

2) The etch depth will be extremely non-uniform, if the amount of exposed Silicon on a wafer exceeds 20 to 30%. For designs with large amounts of open area, the wafer takes on a 'bulls-eye' appearance: A inner circle on the wafer etches differently than an outer circle does

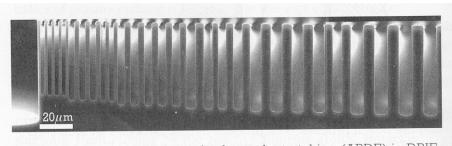

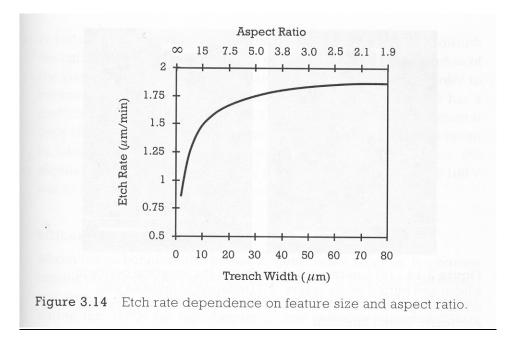

3) Different widths of lines will etch at different rates (this is a local phenomena, not related to the 'bulls-eye' effect). A 2 um wide structure etches much slower than a 20 um wide structure. <u>This is called 'Aspect Ratio Dependant Etching"</u>. This is a fundamental part of DRIE and you can not get around it. You can only design your mask to take this problem into account. Figure 3 shows an example of this process.

4) <u>The masking layers are etched during the deep etch</u>. The by-products of this etching affect the plasma chemistry and will affect the etching of the wafer. Thus a process run with a photoresist mask will have a different etch rate and profile than a process run with a oxide mask.

5) If you are etching to a <u>buried layer or through a wafer</u>, a number of effects can occur: a) the effect of the process recipe changes as amount of Si to be etched changes (becomes less as more of the etched area reaches the desired depth) and b) pedestaling caused by charging of the buried oxide layer. This is an undercut that occurs along the buried oxide/Si interface.

6) If the wafer being etched gets too hot (50C and above), the polymer that has been deposited onto the wafer will desorb. So, <u>a hot wafer will etch isotropically</u>, <u>not anisotropically</u>.

#### Aspect Ratio Dependant Etching

Notice how the etch depth in figure 3.13 becomes less as the width of the open portion of the feature decreases. This is NOT a series of images of etch depth, but rather the result of a single etch. As you can see this is a major effect

**Figure 3.13** Lag or aspect ratio-dependent etching (ARDE) in DRIE. The etch rate decreases with increasing trench aspect ratio. Courtesy of Lucas NovaSensor, Fremont, California.

The above figure is the data from figure 3.13 shown in a different format. Remember, a 100um deep Si etch for a feature 5 um wide has an aspect ration of 20.

## 6.0) General Guidelines for Optimizing the Deep Si Etch Process

The perfect Bosch etch is a balance between the 'right amount' of polymer on the sidewalls and the bottom of the trench and energy and duration of the SF6 etch (polymer and Si). Unfortunately, this 'perfect' balance only occurs for a recipe for a specific mask design and etch depth. Varying either the design or the etch depth will move the process out of this 'perfect window'. The process will need to be modified to either different concentrations of polymer, radicals, and ions (and ion energy). Presently, the new parameters that create the 'perfect balance' are found by trial and error by the user (i.e. you). In the coming months, a general procedure for optimizing DRIE processes will be developed by the NanoFab.

If you need to vary and optimize the process for your mask and etch depth, the parameters that you should initially change are: the RF power (for both Etch and Deposition) and the Etch and Deposition time. These parameters affect the amount of polymer deposited and amount of polymer and Si removed in each step. And are the easiest to change in way that the result is understandable.

Process optimization is required when one of following scenarios occur:

- 1) Changes in mask design (amount of open Si changes)

- 2) Changes in the size of the smallest feature (say from 10 um to 5 um)

- 3) Increased Etch Depth

- 4) Oxide mask etches away too quickly

The oxide mask etches during the C4F8 etch step. C4F8 with ion bombardment etches oxide. Reducing the Bias Voltage during the deposition step should reduce the oxide mask etch rate

# 6.0) Typical Etch Recipe:

Flows, powers and Vbias (and capacitor settings)

## 7.0) Process Parameters

A) To understand how to optimize the etch processes, first we need to define what parameters we can vary and how these parameters affect the etch.

A) Parameters Global Parameters: Total Pressure, ICP Power, Helium pressure, Temperature:

Etch Parameters: SF6 Flow Rate, RF Power (Vbias), Etch Time:

Deposition Parameters C4F8 Flow Rate, RF Power (Vbias), Deposition Time The important parameters from a optimization perspective are the RF power and the times for both the etch and deposition steps.

B) Effect of each Parameter on the Etch Process

<u>Total Pressure:</u> Affects anisotropy. The lower the pressure, the better the anisotropy. However, we are limited to a minimum total pressure of approximately 30 mTorr due to the pumping speed of the turbo pump and the difficulty starting the ICP plasma at pressures lower than this. <u>ICP Power:</u> The degree of radical and ion generation in the plasma. There is a trade-off between the amount of radicals and ions generated and the heat delivered to the substrate. Oxford has used 450W as a compromise for both deposition and etch. I would not change these, unless you wanted to significantly change the process.

<u>Helium Pressure</u>: The helium is used to cool the wafer. It flows over the backside of the wafer, between the chuck and the wafer. The wafer is held in place by mechanical clamps. I would not change this parameter. <u>SF6 and C4F8 Flow Rates</u>: The flow rates for SF6 and C4F8 are determined by the desired residency time of the gas in the chamber. That

is "how long does the gas reside in the system before it is pumped out'. Typically, the residency time should be as short as possible. However, practically the flow rate is determined by the size of the Turbo pump and the cost of the gas (C4F8 is \$0.66/gram). Oxford has set these flows in the range of 25 to 75 sccm. We typically use 50 sccm for both.

<u>Deposition RF Power:</u> The deposition RF power should be low. This RF power is simply to keep a plasma going near the substrate. Lettingthe radicals form the polymer over the wafer surface. Any significant ion bombardment during this step is detrimental to the process. C4F8 with ion bombardment will etch oxide. The energy of the ion bombardment is related to the Bias Voltage (Vbias). For this step you want to keep this voltage much less than 100V.

<u>Deposition Time:</u> The longer the deposition step, the more polymer is deposited and the more thermal oxide masks are etched

<u>Etch RF Power:</u> During the etch, the process requires ion bombardment. To achieve this, the power on the RF chuck should be high enough to get a Bias Voltage higher than 100V. The ions are required to remove the polymer, but not to etch the silicon.

<u>Etch Time</u>: The etch time needs to be long enough for the polymer at the bottom of trench to be removed and enough for the desired depth of Si to be etched, but not too long (i.e. too long and the polymer on the sidewalls is etched and undercut occurs).

# 7.0 Chamber Conditioning

To ensure a repeatable etch process, the 'condition' of the inside of the etch chamber must be consistent. Consistent conditioning means that the areas of the chamber walls coated with polymer or are exposed metal should be the same. The state of the wall (if it is polymer or metal) affects the chemistry (i.e. the radical and ion concentrations) in the plasma and that affects the etch. Following the standard pre-etch plasma cleaning instructions appears to keep the system walls in the proper 'condition'.

Chamber Plasma Clean Recipe:

Power, flow, time, etc